# ATC // AVX MOS Single Layer Capacitors

# Metal Oxide Semiconductor

ATC//AVX Thin Film Technologies offers semi-custom thin film Metal Oxide Semiconductor (MOS) Single Layer Capacitors suitable for RF/ microwave and millimeter-wave applications. The silicon oxide dielectric is fabricated with high temperature processing resulting in excellent uniformity and stability.

ATC//AVX Thin Film Technologies' unique processing and materials sets result in MOS capacitors with high Q, excellent temperature stability, high dielectric strength, high insulation resistance and low ESR. A wide range of termination metallizations are available to facilitate epoxy, solder die attach, thermosonic and ultrasonic bonding and gold or aluminum wire bonding. Custom applications and designs are welcome. Consult factory for additional information.

#### **Benefits**

- Rectangular sizes up to several mm in length (100's mils)

- Square sizes from 254μm x 254μm (10 mils)

- Thicknesses from 50 to 250 µm (2 to 10 mils)

- DC to GHz operation

- High Q

- High Insulation Resistance >1 G-ohm

- Low ESR designs <100 milliohms</li>

# **Typical Electrical Specifications**

| Material              | MOS (SiO <sub>2</sub> ) |

|-----------------------|-------------------------|

| pF/mm² Typical        | 85 @ 50V rated          |

| TCC                   | ±30 ppm/°C              |

| Rated Voltage         | ≤100                    |

| Peak Voltage at +25°C | 1.5 x Rated             |

| DF                    | ≤0.1%                   |

#### **Test Methods**

| Specification | Parameter         | Method or<br>Paragraph |

|---------------|-------------------|------------------------|

| MIL-STD-883   | Bond<br>Strength  | 2011.7                 |

| MIL-STD-883   | Shear<br>Strength | 2019                   |

| MIL-STD-202   | Life              | 108                    |

#### **How to Order**

| <u>MS</u>      | <u>20</u>                                                                |

|----------------|--------------------------------------------------------------------------|

| Series<br>Code | Case<br>Size                                                             |

| MS - MOS       | Square size<br>in mils<br>10, 20, 30, 40<br>OS - special<br>order please |

supply design

| 0               | <u>3</u>                    |

|-----------------|-----------------------------|

| se<br>ze        | Working<br>Voltage          |

| re size<br>mils | Z = 10  WVDO $3 = 25  WVDO$ |

| 30, 40          | 5 = 50  WVDC                |

| pecial          | S - special                 |

| please          | order                       |

| <u>3</u>                                      | <u>S</u>                                 |

|-----------------------------------------------|------------------------------------------|

| rking<br>Itage                                | Dielectri<br>Code                        |

| 0 WVDC<br>5 WVDC<br>0 WVDC<br>special<br>rder | S = SiO <sub>2</sub><br>for MOS<br>style |

| -                       |

|-------------------------|

|                         |

| EIA capacitance         |

| code in pF              |

| First two digits =      |

| significant figures     |

| or R for decimal place. |

| Third digit - number of |

| zeros or after "R"      |

| significant figures.    |

|                         |

100

Capacitance

| M                               |

|---------------------------------|

| Capacitance<br>Tolerance        |

| $J = \pm 5\%$<br>$K = \pm 10\%$ |

M

| $= \pm 5\%$  | 1st    |

|--------------|--------|

| $= \pm 10\%$ | 2nd    |

| $= \pm 20\%$ | layer, |

|              | bondi  |

|              | Top    |

|              | 38     |

|              | Botte  |

|              | 93 - T |

|              | 00     |

| <u>3/23</u> |

|-------------|

| Termination |

| Code        |

1st position top layer

2nd position top bonding

layer, 3rd position bottom

bonding layer, 4th position

Top layers: 37 = AuTaN

38 - AuTiW, 18 - AITiW

Bottom layers: 23 - CrAu

93 - TiWNiAu, 53 = CrNiAu

OSOS - Special Order

Please Supply Design

## W Packaging

W = antistatic waffle pack T= tested whole wafer D - Tested wafer diced on tape

AMERICAN

TECHNICAL

CERAMICS

ATC // AVX Thin Film Technologies tfsales@atceramics.com

ATC North America sales@atceramics.com

ENGINEERS'

CHOICE®

ISO 9001 REGISTERED

COMPANY

# **ATC // AVX MOS Single Layer Capacitors** Metal Oxide Semiconductor

## **Standard Wafers Offered and Thickness**

N+ (Arsenic doped); 0.001-0.005 Ohm-cm resistivity; ≥100µm thick N++ (Phosphorous doped): .001 to .0015 Ohm-cm resistivity; ≥100µm thick

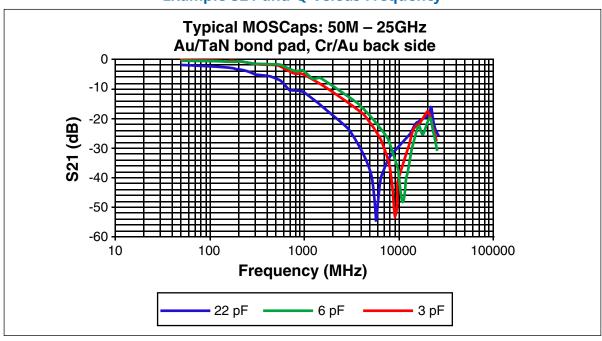

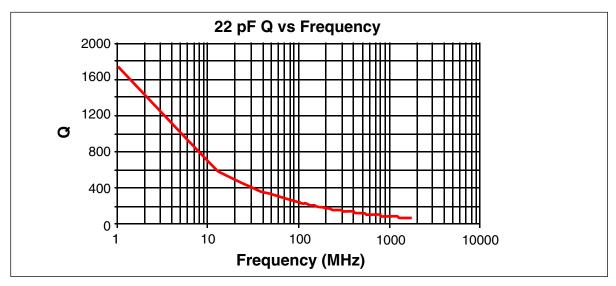

## **Example S21 and Q Versus Frequency**

Sales of ATC products are subject to the terms and conditions contained in American Technical Ceramics Corp. Terms and Conditions of Sale (ATC document #001-992 Rev. A 10/03). Copies of these terms and conditions will be provided upon request. They may also be viewed on ATC's website at www.atceramics.com/productfinder/default.asp. Click on the link for Terms and Conditions of Sale. ATC has made every effort to have this information as accurate as possible. However, no responsibility is assumed by ATC for its use, nor for any infringements of rights of third parties which may result from its use. ATC reserves the right to revise the content or modify its product line without prior notice.

© 2010 American Technical Ceramics Corp. All Rights Reserved.

ATC # 001-1088 Rev. A; 5/10

AMERICAN

TECHNICAL

CERAMICS

ATC // AVX Thin Film Technologies **ATC North America** tfsales@atceramics.com

sales@atceramics.com

ENGINEERS' CHOICE® ISO 9001 REGISTERED COMPANY

THE ENGINEERS' CHOICE™

www.atceramics.com