# **Selecting RF Chip Capacitors for Wireless Applications**

With today's advancements in wireless technology, greater emphasis is being placed on component performance. This article will provide a discussion of ceramic and porcelain chip capacitors and understanding their behavior in RF product designs. They are an excellent choice for wireless applications where volumetric efficiency, reliability and RF performance are an absolute must.

#### **DESIGN CRITERIA**

The most commonly used design categories for ATC ceramic chip capacitors are the multilayer (MLC) and single layer (SLC). The MLC employs multiple or stacked electrode sections while the SLC consists of two electrodes separated by a dielectric. Both are constructed with the following design criteria:

- Ceramic and porcelain dielectrics

- Rugged hermetic construction

- Optimized electrode patterns

- Low resistivity electrode and termination materials

- High dielectric strength

- Protective barrier layer between electrodes and termination (MLC)

- Fabricated for direct surface mounting on microstrip

- Ultra stable with temperature and humidity

- Extremely high Q

- Low dissipative losses

## **SELECTING A SUITABLE CAPACITOR**

When selecting ceramic chip capacitors for use in RF wireless applications, it is important to establish overall circuit performance criteria. The component should then be matched to the specific application requirement. A typical shopping list of performance requirements for this circuit element may include the following:

- Capacitance (pF)

- Tolerance (%)

- Voltage Rating (WVDC, VRMS)

- Equivalent Series Resistance (ESR)

- Temperature Coefficient (TC, PPM/°C)

- Dissipation Factor (%)

- Series Resonant Frequency (Fsr)

- Parallel Resonant Frequency (Fpr)

- Insulation Resistance (IR)

- Dielectric Aging Effects (% per decade hr.)

#### **PERFORMANCE**

An ideal capacitor stores all of its energy in the dielectric, as 1/2CV<sup>2</sup>. However, a realizable capacitor will always exhibit some series resistance that must be taken into account. This series resistance referred to as Equivalent Series Resistance (ESR) is always one of the most essential factors to consider in an RF circuit design. It is attributed mainly to the contribution of dielectric losses, and metal losses of electrode and termination materials. Also, the manufacturing process must be properly controlled during every phase to insure optimal ESR performance. At low frequencies, Hz to KHz region, the main contributor to ESR is dielectric loss. However, at RF frequencies the ESR is due mainly to the metal losses, i.e., electrodes and terminations. These losses become significant because of skin effect and increase proportionally as the square root of frequency.

ESR is typically expressed in milliohms at specific frequencies by most manufacturers. The standards most frequently used as a guideline are EIA RS483 and MIL-C-55681. The measurements are performed at various frequencies between 30 MHz and 1 GHz. Therefore, it is necessary to consider the ESR value at your specific design frequency. If, for example, you are designing for a 900 MHz wireless application, and the ESR is specified at 150 MHz, the ESR at 900 MHz may be calculated by multiplying the specified ESR at 150 MHz by  $\sqrt{900/150}$ . This relationship is well behaved at RF and accounts for the "skin effect". The ESR is the main loss element of the capacitor and is used to determine the power loss i.e.;  $P = I^2 \times ESR$ .

Quality Factor (Q) is a figure of merit and is a measure of a capacitor's ability to store energy in its dielectric. Since Q = Xc/ESR, it becomes evident that low ESR yields high Q. As with ESR, the Q must be specified or calculated at the design frequency.

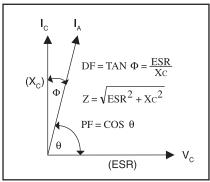

Dissipation Factor (DF) is also referred to as the loss tangent and is the reciprocal of Q, i.e., DF = 1/Q. With an ideal capacitor the current leads the voltage by 90 degrees. However, actual capacitors will have a small angle referred to as the loss angle. The tangent of the loss angle is equal to the dissipation factor and indicates what portion of the total reactive power in the capacitor will be lost as heat i.e., dissipative loss.

Example: loss angle = 3 degrees;

therefore DF =  $\tan 3 = 0.05$  or 5%.

In the above example, the dissipation factor is 0.05 or 5%. This means that 5% of the total power in the capacitor is lost as heat. Refer to Fig. 1.

AMERICAN

ATC North America sales@atceramics.com

TECHNICAL

ATC Europe saleseur@atceramics.com

CERAMICS

ATC Asia sales@atceramics-asia.com

HE ENGINEERS' CHOICE® ISO 9001 REGISTERED The ATC 100 Series

porcelain chip capacitors

have a loss tangent less

than 0.0001 that yields

a Q greater than 10,000.

In this instance the dissi-

pative losses are less

than 0.01%. This is de-

sirable for optimum per-

formance in an RF

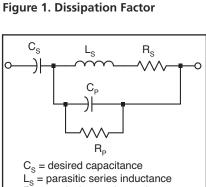

$\bar{R_S}$  = equivalent series resistance circuit. An amplifier cir- $C_p$  = parasitic parallel capacitance cuit for example, that  $R_{\rm p}$  = parallel resistance utilizes a high Q, low ESR (DF) capacitor will Figure 2. Equivalent Circuit Model realize a significant increase in the effective gain. Battery life for portable devices is also

extended with the use of low loss capacitors. An easy way to relate ESR, DF and Q together is: ESR = Xc DF = Xc/Q

DF = ESR/XcQ = Xc/ESR

## **PARASITIC BEHAVIOR**

Another major concern in wireless design applications is the parasitic behavior of the reactive elements. Capacitors may be modeled with equivalent circuit elements that account for the parasitic effects. Figure 2 shows a lumped element model and is valid for chip capacitors in these applications. Using this model can help the designer determine such characteristics as the series resonant frequency (Fsr), equivalent series inductance (ESL) and transfer function characteristics

It is necessary to consider the functional application, e.g., coupling, bypass, timing etc., and layout in the circuit. For example, a given application may require a capacitor for interstage coupling. A more thorough view of parasitic behavior is accomplished by the use of scattering parameters. ATC specifies S-Parameter performance for their capacitor line. This data may be downloaded from ATC's website and is also available on ATC's CD Catalog.

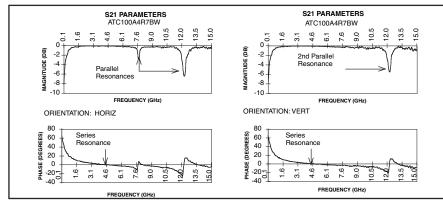

Figure 3. S-Parameter Plots comparing horizontal and verticalmounting orientations

In the above example it is important to evaluate the S-Parameter performance for the subject capacitor. If a parallel resonance occurs at or near the frequency band of interest, this capacitor will serve to attenuate the RF energy rather than it's intended coupling function. S-Parameter data will show such characteristics as parallel resonance, series resonance, insertion loss, insertion phase, return loss magnitude and return loss phase. A full set of S-Parameters may be used in conjunction with design simulation software, and is generally presented as a forward and reverse two port measurement known as an S2P file.

### **COMPONENT ORIENTATION**

Chip capacitors are usually surface mounted on a microstrip. They can be mounted with the electrodes parallel or perpendicular to this microstrip. In the above example a coupling capacitor is used between stages. As previously mentioned it is essential that parallel resonances do not occur in the frequency band of interest. By mounting the capacitor vertically, that is, with the electrodes perpendicular to the microstrip, the first parallel resonance will not be present thereby significantly extending the usable bandpass. A comparison of the two mounting orientations using S-Parameters is shown in Figure 3.

Series Resonant Frequency: Occurs at the frequency corresponding to 0 degrees phase of S21; also S21 magnitude has minimum loss at this frequency equal to ESR.

Parallel Resonant Frequencies: Are observed as a sharp attenuation in the S21 magnitude while S21 phase has rapid transitions through 0 degrees corresponding to each parallel resonance. Vertical mount ing optimizes this performance.

S21 Magnitude 3DB Frequency: Capacitance value may be verified at this frequency by C = 0.159/100 \* F (Hz).

Richard Fiore is a Director of RF Applications Engineering at American Technical Ceramics Corp. In Huntington Station, NY.

Sales of ATC products are subject to the terms and conditions contained in American Technical Ceramics Corp. Terms and Conditions of Sale (ATC document #001-992 Rev. B 12/05). Copies of these terms and conditions will be provided upon request. They may also be viewed on ATC's website at www.atceramics.com/productfinder/default.asp. Click on the link for Terms and Conditions of Sale.

ATC has made every effort to have this information as accurate as possible. However, no responsibility is assumed by ATC for its use, nor for any infringements of rights of third parties which may result from its use. ATC reserves the right to revise the content or modify its product without prior notice.

© 1996 American Technical Ceramics Corp. All Rights Reserved.

ATC # 001-821; Rev. D 10/05

MERICAN CERAMICS TECHNICAL **ATC Europe** ATC Asia

**ATC North America** sales@atceramics.com

saleseur@atceramics.com

sales@atceramics-asia.com